HW/SW and System-Level

Early HW/SW Integration and Validation

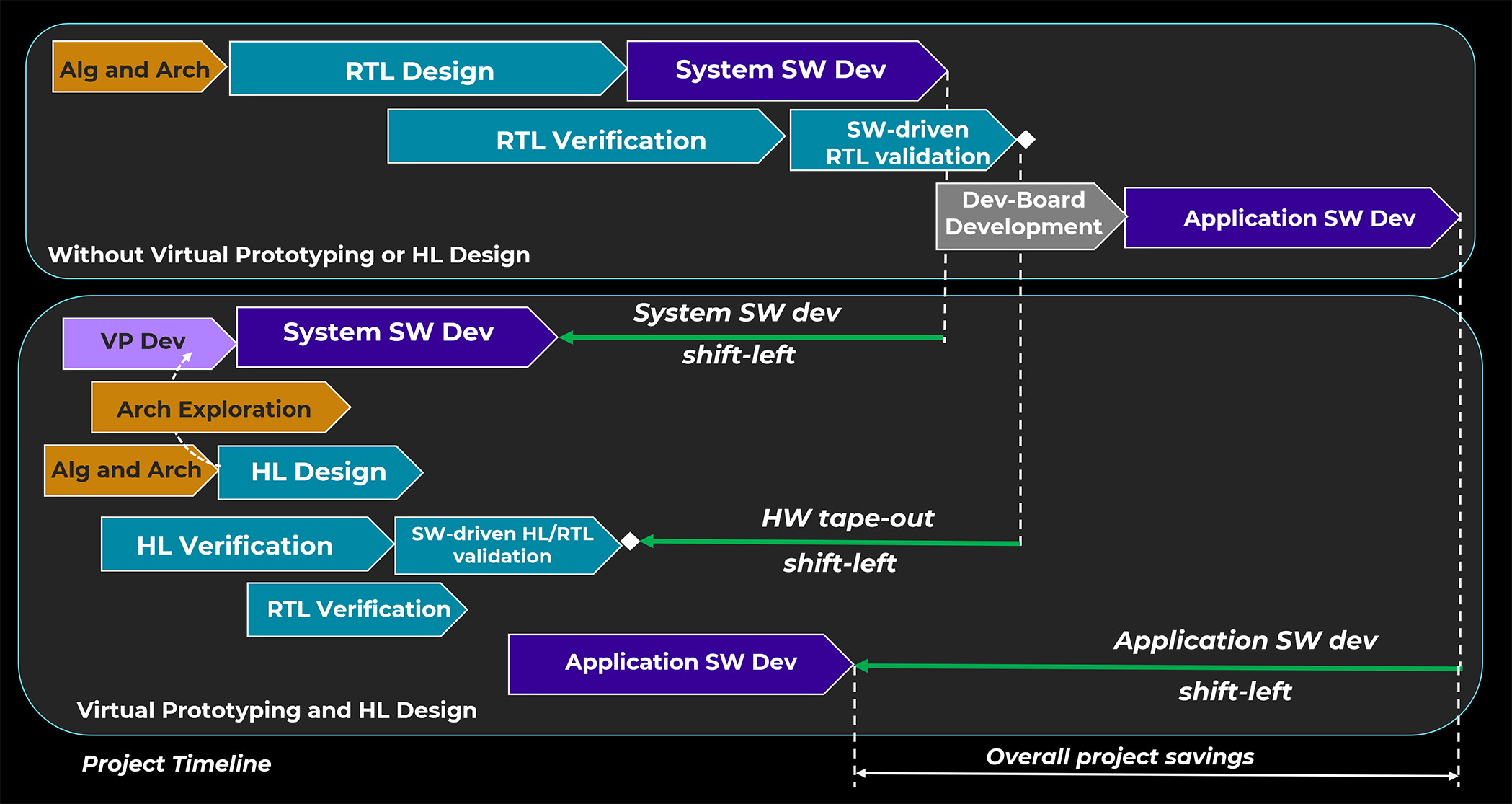

In traditional chip development, hardware and system software often proceed sequentially.

Software teams wait for RTL to stabilize before they can begin meaningful development and testing, and when hardware becomes available it requires prototyping boards or emulation infrastructure due to RTL simulation speeds.

Teams that use virtual platforms to bridge this gap face a different problem. Those models are hand-built and maintained separately from the hardware design, and as hardware evolves and specifications are updated the virtual platform can drift or become a burden to maintain as a separate model throughout the project.

Rise eliminates both problems. The high-level executable specification that drives the Rise hardware design flow can also be used as the software-ready model as it runs orders of magnitude faster than RTL.

Hardware and software teams work in parallel from day one and throughout the project from the same source of truth for the hardware functionality.

A Hardware-Accurate Model Ready for Virtual Platform Integration

The high-level executable specification model can take multiple forms in C++ or SystemC, but one of the most commonly used for today’s virtual platforms is a SystemC TLM-2.0 wrapped model with latency, throughput, and interface timing annotated directly from the high-level synthesis RTL simulation results. It is an accurate reflection of the hardware behavior, performance numbers annotated from the RTL, and runs orders of magnitude faster than an RTL simulation. This combination of accuracy and speed enables both early software bring-up and detailed HW/SW system performance analysis.

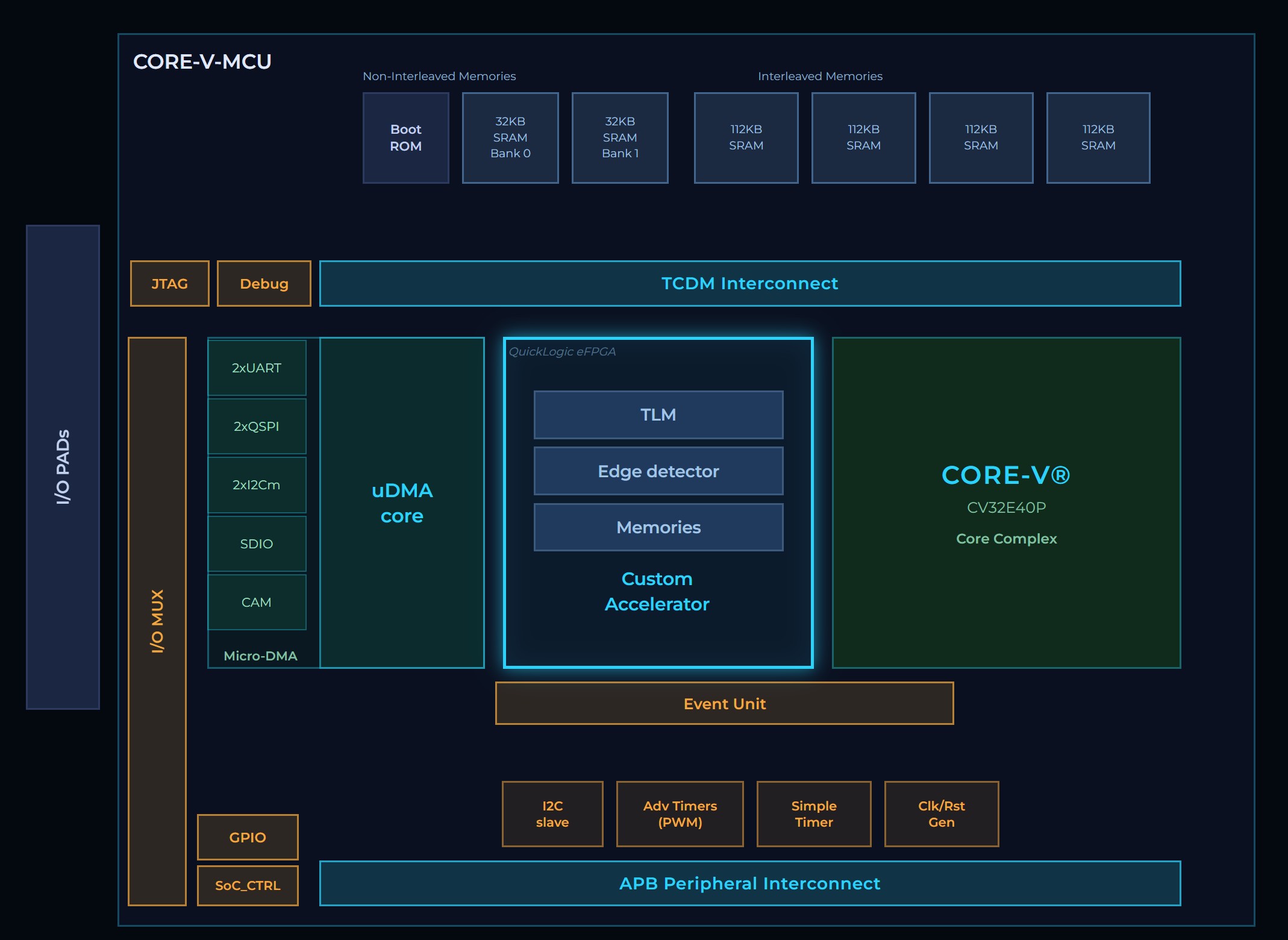

Rise has already put this design flow into practice, integrating the high-level model into industry-standard virtual platforms using the TLM-2.0 standard. As a demonstration, Rise has collaborated with CircuitSutra, who developed a RISC-V virtual platform in partnership with the OpenHW Group. It is a demonstration vehicle showing how a custom hardware accelerator can be seamlessly added to the RISC-V CPU core and HW/SW interactions and performance validated with a virtual platform. This demonstration vehicle is available to prospective customers who want to see the complete HW/SW co-design flow in action.

Explore Architecture and Validate Integration Before Committing to RTL

The earlier an architectural problem is found, the cheaper it is to fix. The Rise HL model enables full-system HW/SW co-simulation from the earliest stages of the design process, giving hardware and software teams a shared environment in which to explore micro-architecture options, detect system bottlenecks, and validate interface behavior.

Hardware architects can rapidly evaluate how different memory architectures, pipeline configurations, and interface choices affect system-level throughput and latency, with software running against the model providing realistic stimulus that manual testbenches rarely achieve. This parallel workstream transforms HW/SW co-design from a late-stage integration event into an ongoing collaborative process.

See the Complete HW/SW Co-Design Flow in Action

Watch how Rise integrates a custom hardware accelerator into an industry-standard virtual platform, demonstrating the complete HW/SW co-design flow from executable specification to fully integrated system.

Webinar: Virtual Prototype + High Level Synthesis — Advanced D&V Flow for RISC-V Based SoC – Integration starts around 25min mark